TSMC представила новое поколение транзисторных технологий на конференции IEEE International Electron Device Meeting в Сан-Франциско. Технология N2 (2-нанометра) станет первым шагом компании в направлении новой транзисторной архитектуры, известной как нанолистовая или gate-all-around.

По сравнению с текущим передовым 3-нанометровым процессом N3, новая технология обеспечивает увеличение производительности до 15% или снижение энергопотребления до 30%, при повышении плотности на 15%.

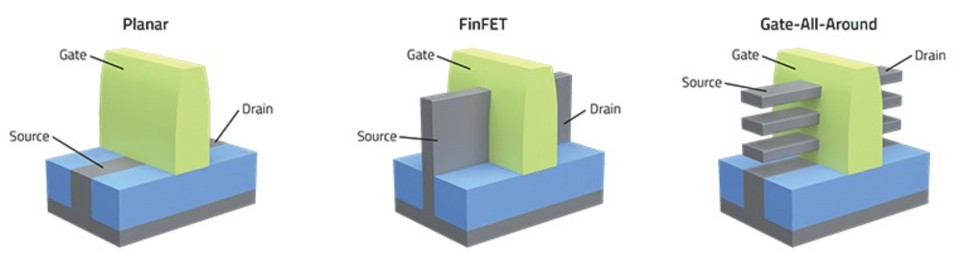

Как отметил вице-президент TSMC по исследованиям и разработкам Джеффри Йип, N2 является результатом более чем четырехлетней работы. В отличие от современных FinFET транзисторов с вертикальным кремниевым ребром, нанолистовые транзисторы имеют стопку узких кремниевых лент.

Новая архитектура не только обеспечивает лучший контроль тока, но и позволяет создавать более разнообразные устройства за счет изменения ширины нанолистов. Технология Nanoflex от TSMC позволяет размещать на одном чипе логические ячейки с разной шириной нанолистов.

Особенно важным достижением стало улучшение характеристик SRAM-памяти. N2 демонстрирует рекордную плотность в 38 мегабит на квадратный миллиметр, что на 11% превышает показатели предыдущего поколения.

Исследователи Intel также представили оптимистичный взгляд на будущее технологии. Им удалось создать работоспособный транзистор с длиной затвора всего 6 нм и толщиной нанолиста 3 нм, что существенно превосходит ранее предполагаемый предел масштабирования в 10 нм.

По словам Санджая Натараджана, старшего вице-президента Intel, это доказывает, что технологические ограничения еще не достигнуты, и кремниевые нанолистовые транзисторы имеют значительный потенциал для дальнейшего развития.