Один из инженеров тайваньской компании TSMC, известный как Dr. Kim, поделился информацией о существенном прогрессе в разработке 2-нанометрового техпроцесса. По его словам, команде удалось повысить выход годных тестовых чипов на 6%, что позволит сэкономить миллиарды долларов будущим клиентам компании.

Новый 2-нм техпроцесс TSMC (N2) станет первым, использующим транзисторы с круговым затвором (GAA) на основе наностраниц. Эта технология обещает значительное снижение энергопотребления, повышение производительности и плотности размещения транзисторов по сравнению с текущим 3-нм процессом.

По предварительным данным, микросхемы, произведенные по технологии N2, будут потреблять на 25-30% меньше энергии при той же частоте работы. Производительность вырастет на 10-15%, а плотность размещения транзисторов увеличится на 15% по сравнению с текущим техпроцессом N3E.

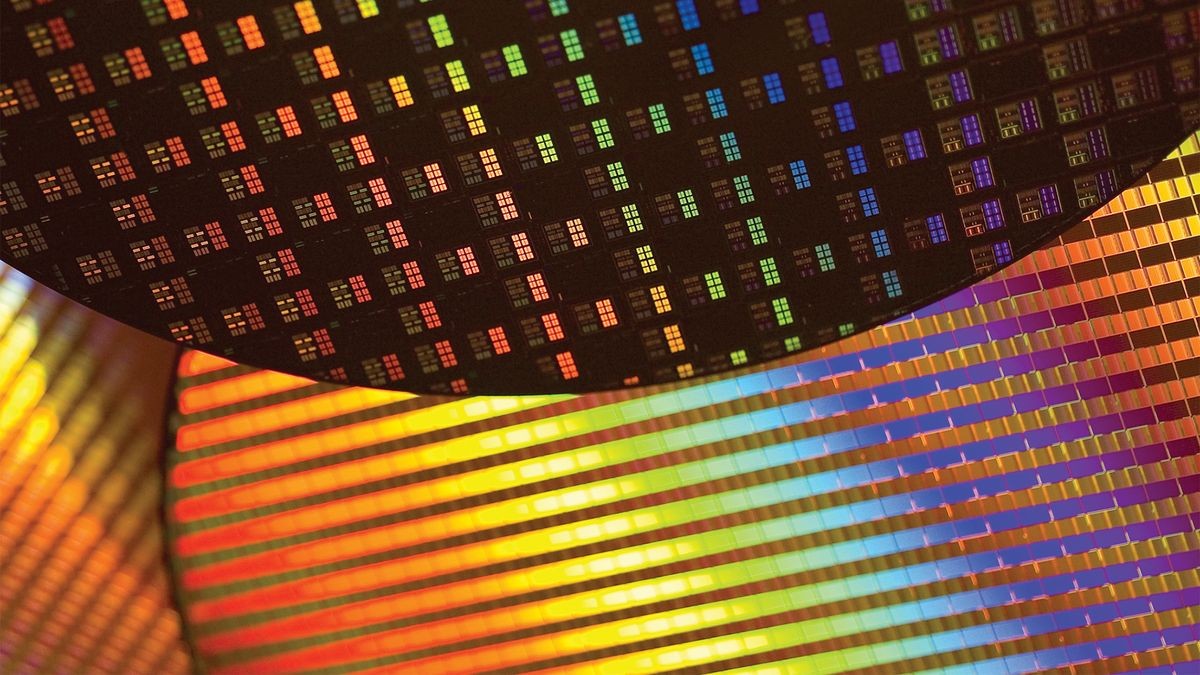

Массовое производство 2-нм чипов планируется начать во второй половине 2025 года. До этого времени TSMC продолжит работу над улучшением технологии и снижением количества дефектов. Тестовые пластины для клиентов станут доступны с января следующего года.

Стоит отметить, что Dr. Kim не уточнил, касается ли достигнутое улучшение выхода годных тестовых чипов памяти SRAM или логических схем. Однако любое повышение выхода годной продукции напрямую влияет на стоимость производства и, соответственно, конечную цену для заказчиков.